Introdução

O layout PCB fontes é o ponto de partida para qualquer projeto de alimentação confiável e conforme. Neste artigo abordaremos desde conceitos fundamentais (diferença entre fontes lineares e fontes SMPS) até requisitos normativos (IEC/EN 62368-1, IEC 60601-1), estratégias de mitigação de EMI, e melhores práticas para ground plane, creepage/clearance e gestão térmica. Engenheiros de projeto, integradores e gerentes de manutenção encontrarão aqui recomendações práticas, exemplos calculados (V = L·di/dt), e referências a padrões e métricas como PFC, MTBF e limites de temperatura.

Para quem busca aprofundar tópicos específicos, consulte a biblioteca técnica da Mean Well Brasil e outros artigos no blog. Para mais artigos técnicos consulte: https://blog.meanwellbrasil.com.br/

O que é layout PCB fontes: conceitos fundamentais e terminologia que você precisa dominar

Definição essencial

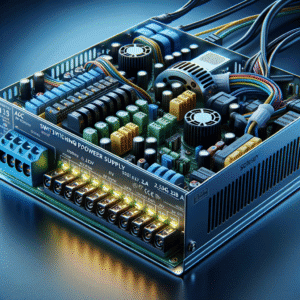

O layout PCB fontes refere-se à disposição física de componentes, traçados, planos de referência e vias em uma placa onde a fonte de alimentação (principalmente SMPS) opera. Inclui o mapeamento de nós críticos como switching node, entrada/saída de potência, pontos de medição e conexões de terra.

Diferenciação entre tecnologias

Fontes lineares têm caminhos de corrente simples e menos preocupação com di/dt, enquanto chaveadas (SMPS) apresentam nós de alta di/dt e exigem atenção ao tamanho do loop de comutação e à indutância parasita. Termos-chave: ground plane, creepage, clearance, di/dt, switching node, EMI/EMS (IEC 61000 series).

Diagrama de blocos e pontos críticos

Um diagrama simplificado de blocos (retificador → PFC → conversor → saída) ajuda a localizar pontos críticos: entradas de rede, indutor principal, MOSFETs/IGBTs, capacitores Cin/Cout e sense resistors. Priorize rotas curtas e áreas de loop pequenas para os nós de potência para reduzir EMI e queda de tensão.

Por que o layout PCB fontes importa: impacto em desempenho, EMI/EMC, eficiência e segurança

Relação layout → EMI/EMC

A área do loop de comutação é proporcional à emissão radiada; reduzir a área reduz o campo magnético gerado. Regra prática: diminuir a área do loop de entrada do switching node reduz EMI na faixa de MHz de forma significativa. Fórmula útil: Vinduzido = L_parasita × di/dt.

Impactos na eficiência e regulação

Traços longos e de baixa largura aumentam resistência (I²R), provocando queda de tensão e perda térmica. Isso afeta a regulação de saída e o ripple. Escolhas no layout (traços grossos, planos de cobre e vias múltiplas) melhoram eficiência e MTBF, especialmente em cargas elevadas.

Exemplos reais de falhas por layout

Casos de campo mostram reinicializações intermitentes por desacoplamento mal posicionado; falhas por superaquecimento quando vias térmicas insuficientes. Não conformidades EMC em testes (IEC 61000-4-3 suscetibilidade) frequentemente rastreiam-se até routing de sinais de alta di/dt ou planos de terra mal particionados.

Requisitos elétricos, térmicos e normativos para layout PCB fontes

Requisitos normativos e certificações

Projetos devem considerar IEC/EN 62368-1 (áudio/video e TI), IEC 60601-1 (equipamentos médicos) e normas EMC como IEC 61000-4-2/3/4/6. Para aplicações industriais e telecom, verifique IEC 61000-3-2 (flicker e harmônicos) e requisitos de segurança UL/CSA quando aplicável.

Distâncias de creepage/clearance e classes de isolamento

Use tabelas de referência para creepage/clearance conforme tensão de pico. Exemplo prático (valores típicos — confirmar norma aplicável para cada projeto):

- 150 VAC contínuo → clearance ≈ 3.0 mm, creepage dependendo do material.

- 300 VAC → clearance ≈ 6.0 mm.

A seleção do material do PCB (CTI) e a classe de isolamento influenciam essas distâncias.

Critérios elétricos e térmicos

Inclua derating para capacitores (fator de redução de capacitância com temperatura), segurança em capacitores X/Y para EMI, fusíveis e limites de temperatura (Tjunction, Tmax do PCB). Calcule correntes máximas, margem de duty cycle e MTBF com base em temperaturas operacionais reais e perfil térmico.

Projetar planos de terra e gestão de retorno: regras para layout PCB fontes com baixo ruído

Ground plane contínuo vs. split

Um ground plane contínuo oferece baixa impedância para retorno de sinais, mas em fontes SMPS pode ser necessário um split controlado entre terra analógica e terra de potência. Use pontes de baixa impedância (shunts ou tags curtas) para conectar zonas e evitar loops.

Regras de retorno de corrente

Retorno de correntes de alta di/dt deve seguir o mesmo caminho físico do traço de ida; mantenha os traços de alta corrente sobre o plano de terra correspondente para minimizar loop area. Evite que correntes de potência atravessem áreas de terra analógico sensível.

Técnicas de star-ground e pontos de conexão

Para sensores e shunts, implemente star-ground onde um ponto único de referência liga sistemas à terra comum. Para conexões externas de alto di/dt (barras, bornes), use faixas de cobre reforçadas e pontos de solda próximos ao plano para reduzir impedância de aterramento.

Posicionamento de componentes e roteamento crítico para layout PCB fontes

Prioridades de posicionamento

Coloque primeiro: diodos/ponte retificadora e EMI filter na entrada; depois interruptores (MOSFETs/IGBTs), indutores, capacitores de saída (Cout) e sensores de corrente. Capacitores Cin devem estar o mais próximo possível do retificador/primário do conversor.

Regras para nós de alta di/dt

Mantenha os componentes do loop de comutação (MOSFET, diodo de recuperação, indutor, capacitores) em uma disposição compacta com traços curtos e espessos. Minimize vias dentro do loop; cada via adiciona indutância parasita.

Sensores de corrente e aterramento de singulares

Coloque shunts e sensores de corrente longe de nós de salto de potencial alto; rotas de retorno devem ser isoladas de planos de potência para não introduzir ruído nas medições. Utilize filtros RC locais e buffers para sinais de medição sensível.

Filtragem, desacoplamento e técnicas de mitigação de EMI no layout PCB fontes

Posicionamento de capacitores Cin/Cout e desacoplamento

Capacitâncias de entrada (Cin) devem ficar adjacentes ao conector de entrada/retificador; capacitâncias de saída (Cout) justo na saída do indutor/transformador. Os capacitores de desacoplamento de alta frequência (cerâmicos) devem estar imediatamente ao lado dos pinos dos MOSFETs para reduzir impedância em altas frequências.

Uso de capacitores X/Y e chokes

Capacitores X (entre fase e neutro) e Y (linha/terra) em filtros EMI devem ser montados conforme o trajeto de corrente previsto e com gaps de creepage/clearance apropriados. Chokes common-mode são eficazes para suprimir ruído diferencial e comum — ubique-os na entrada antes do resto do circuito.

Estratégias combinadas layout+componente

Combine layout otimizado com componentes: traços curtos para capacitores, vias múltiplas para planos de terra, e rotas diferentes para common-mode e differential-mode. Teste em câmaras EMC e ajuste o filtro (capacitores/indutores) para as bandas críticas identificadas.

Stack-up, espessura de cobre e gestão térmica no layout PCB fontes

Escolha de stack-up e espessura de cobre

Para 2 camadas: use traços largos e planos de cobre pesado (2 oz) para trilhas de potência. Para 4/6 camadas: dedique uma camada inteira como plano de terra e outra para plano de potência para dissipação e roteamento. O aumento da espessura do cobre reduz I²R e melhora a gestão térmica.

Dimensionamento de vias térmicas

Vias térmicas sob pads de MOSFETs/ICs devem ser numerosas e dispostas em matriz para transferir calor para planos internos ou o outro lado do PCB. Use vias com diâmetro e plating adequados (ex.: vias 0.3–0.5 mm, tentadas conforme processo) e estime resistência térmica via ANSYS/Flotherm ou cálculos conservadores.

Cálculo prático de temperatura e derating

Calcule dissipação (Pd = I²·Rds_on para MOSFETs, perdas no indutor) e estime ΔT = Pd·RθJA. Aplique derating: opere componentes abaixo de 80% de sua corrente nominal em ambientes com refrigeração limitada. Use planos de cobre como dissipadores e heat-spreader quando sem heatsinks mecânicos.

Checklist de validação, erros comuns e próximos passos para o seu layout PCB fontes (resumo estratégico e aplicações)

Checklist prático de validação

- Verifique creep/clearance conforme norma aplicável.

- Confirme loop area mínimo para switching node.

- Meça impedância de retorno e vias térmicas suficientes.

- Teste EMI em pré-conformidade (EMI chamber) e verifique suscepibilidade IEC 61000.

Erros comuns e correções rápidas

Erros típicos: capacitores Cin mal posicionados, splits de ground mal conectados, vias insuficientes em pads térmicos. Correções rápidas: mover capacitores, adicionar vias, criar ponte de terra de baixa impedância, rever roteamento do sensing.

Recomendações por aplicação e próximos passos

Para drivers LED, telecom e industrial adote layout robusto com PFC ativo quando requerido e tolerância térmica. Para necessidade imediata de módulos prontos, considere módulos SMPS encapsulados da Mean Well; para aplicações que exigem essa robustez, a série de fontes AC-DC da Mean Well é a solução ideal: https://www.meanwellbrasil.com.br/produtos. Para soluções open-frame e OEM, avalie as séries LRS/RSP: https://www.meanwellbrasil.com.br/

Conclusão

O sucesso do projeto do seu produto depende tanto da escolha do topology da fonte quanto da qualidade do layout PCB fontes. Seguindo regras de posicionamento, gestão de terra, filtragem e térmica você reduz risco de não conformidade EMC, melhora eficiência e aumenta a vida útil do sistema (MTBF). Consulte padrões aplicáveis (IEC/EN 62368-1, IEC 60601-1, IEC 61000 series) durante todo o processo de projeto.

Se quiser, posso transformar este esqueleto em um pacote técnico (PDF/OnePager) com checklists exportáveis, diagramas de referência e exemplos de stack-up para 2/4/6 camadas. Para leitura complementar veja também estes artigos: https://blog.meanwellbrasil.com.br/controle-de-emi e https://blog.meanwellbrasil.com.br/pfc-e-eficiencia

Perguntas, dúvidas de aplicação ou casos específicos? Comente abaixo ou traga seu esquema de layout para uma revisão técnica passo-a-passo — queremos ajudar a garantir conformidade e desempenho.