Introdução

No contexto de projeto eletrônico profissional, estabilidade e ruído em PCBs são variáveis determinantes para desempenho, EMC e confiabilidade do produto. Neste artigo abordarei conceitos chave como SNR, floor noise, jitter, target impedance, além de estratégias de PDN, filtragem EMI e desacoplamento para que seu projeto PCB atinja requisitos funcionais e normativos (ex.: IEC/EN 62368-1, IEC 60601-1, IEC 61000-4-x).

A linguagem aqui é técnica: falarei diretamente com engenheiros, projetistas OEM, integradores e equipes de manutenção industrial, oferecendo métricas mensuráveis, checklists e referências práticas para reduzir retrabalho e acelerar certificação. Para mais leituras técnicas consulte: https://blog.meanwellbrasil.com.br/.

O que é estabilidade e ruído em PCBs — conceitos e métricas essenciais para estabilidade e ruído em PCBs

Definição e termos essenciais

Estabilidade em uma placa refere-se à resposta do circuito a variações de carga e tensão ao longo do tempo — isso envolve transient response, margem de ganho-fase e comportamento frente a laços de realimentação. Ruído é qualquer componente espectral indesejado (ruído térmico, switching spurs, EMI conduzida/radiada) que degrade SNR ou provoque erros digitais/analógicos.

Métricas práticas incluem target impedance da PDN (Ω por faixa de frequência), floor noise (dBm/Hz), jitter (ps RMS para sinais de clock) e MTBF para impactos de confiabilidade. Essas métricas traduzem-se diretamente em requisitos de especificação do produto.

Compreender essas grandezas permite identificar se um sintoma — picos nas linhas de alimentação, erros CRC, falhas intermitentes — é causado por falta de desacoplamento, mal roteamento de retorno ou por acoplamento radiado.

Por que essas métricas importam

Sem definição clara de target impedance, o desacoplamento é "adivinhado" e o produto corre risco de falha em testes de conformidade EMC. Normas como IEC 61000-4-6 (imunidade a distúrbios conduzidos) e IEC/EN 62368-1 orientam limites de design e testes.

A medição do floor noise em domínios relevantes (kHz a GHz) orienta a seleção de filtros e topologias de aterramento. PFC em fontes também impacta a forma de onda de alimentação e o espectro de ruído condutivo, exigindo soluções PDN apropriadas.

Ao final, traduzimos essas métricas em requisitos de projeto e critérios de aceitação para produção: limites de jitter para interfaces de alta velocidade, limites de ripple para reguladores, e metas de impedância para o PDN.

Por que controlar ruído e garantir estabilidade importa no seu projeto PCB

Impactos no desempenho funcional

Ruído e instabilidade degradam conversores A/D, causam erros em comunicação serial de alta velocidade e aumentam latência em malhas de controle. Em aplicações médicas, por exemplo, ruidosidade pode comprometer leituras sensíveis e certificação segundo IEC 60601-1.

Além do comportamento elétrico, ruído elevado pode mascarar falhas iniciais e reduzir a vida útil de componentes, afetando MTBF e custos de manutenção. Em conversores DC-DC, resposta transiente pobre aumenta stress térmico em capacitores e indutores.

Controlar ruído melhora SNR, reduz retransmissões em redes industriais e protege integridade de dados em sistemas críticos de automação.

Relevância para EMC, confiabilidade e negócios

Do ponto de vista de EMC, ruído mal contido pode resultar em reprovação de produto nos ensaios de emissão radiada ou condução, atrasando lançamentos e gerando custos com redesign. Investimentos em layout, filtragem e PDN são frequentemente menores que custos de não conformidade.

Do lado da confiabilidade, práticas de estabilidade reduzem falhas intermitentes que são difíceis de replicar, reduzindo NTF (no trouble found) e retrabalhos em campo. Isso tem impacto direto em SLA e custos de garantia.

Em suma, priorizar estabilidade e mitigação de ruído é um trade-off técnico-econômico favorável para produtos comerciais e industriais.

Fontes de ruído e caminhos de acoplamento — diagnóstico prático para estabilidade e ruído em PCBs

Fontes comuns de ruído

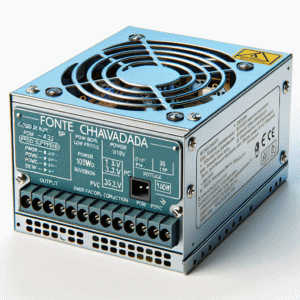

Principais geradores: conversores chaveados (buck/boost), drivers MOSFET/IGBT, sinais de alta velocidade (PCIe, USB, Ethernet), clocks e relés. Ruídos também surgem de fontes externas (rede elétrica com harmônicos devido a PFC).

Componentes passivos degradados (capacitores com ESR elevado) ou layout com vias inadequadas elevam o floor noise. Até mesmo ruídos térmicos em resistores de precisão podem afetar medições sensíveis.

Identificar a fonte é o primeiro passo para correção eficaz; nem todo ruído exige filtro — às vezes a solução é isolar o plano de referência ou ajustar a topologia de alimentação.

Caminhos de acoplamento e checklist de inspeção

Acoplamento pode ser: capacitivo (entre trilhas adjacentes), indutivo (laços de corrente), condutivo (sobre PDN) ou radiado (vias/edges sem blindagem). Cada mecanismo requer abordagem distinta.

Checklist rápido para diagnóstico:

- Verificar laços de retorno e continuidade dos planos de referência.

- Checar posicionamento de capacitores de desacoplamento (menor indutância possível).

- Inspecionar vias de alimentação e stitching de plano.

- Identificar proximidade entre fontes de alta dV/dt e linhas sensíveis.

Essa inspeção orienta medições com escopo diferencial e sonda de campo.

Como medir e quantificar instabilidade e ruído na placa — ferramentas, técnicas e métricas

Ferramentas essenciais e configuração

Equipamentos chave: osciloscópio diferencial de banda larga, analisador de espectro, sonda de campo (near-field probe) e testador de integridade de potência (PDN analyzer). Use probes com baixa capacitância em sinais sensíveis para evitar carga do circuito.

Para medições de integridade de sinal, eye diagrams, jitter analysis e S-parameters (com VNA) são valiosos. Para potência, medir target impedance por faixa de frequência define necessidade de desacoplamento.

Configure o banco de provas com referências de terra adequadas (evite loops de terra), utilize terminadores adequados nas linhas de alta velocidade e registre a posição física da sonda para reprodutibilidade.

Armadilhas de medição e como evitá-las

Medições mal feitas (ground clip longo, sondeamento em ponto errado) geram artefatos que confundem diagnóstico; sempre use sonda diferencial quando a referência não é o terra do chassi. Evite medições apenas no conector de alimentação — iterar por pontos na placa.

Use estímulos controlados: cargas step para testar transient response, swept sine para verificar impedância ao longo da banda. Para EMI, varredura com near-field probe ajuda a localizar pontos de emissão máxima antes de testes anecoicos.

Documente resultados com captura de tela e coordenadas do ponto testado para correlacionar alterações de layout com melhoria de ruído.

Estratégias de layout e PDN para estabilidade e baixo ruído no projeto PCB estabilidade e ruído em PCBs

Regras de layout essenciais

Implemente hierarquia de planos: plano de potência contínuo e plano de referência adjacente reduzem indutância de loop. Separe domínios de sinal: analógico, digital e power com retorno de corrente cuidadosamente planejado.

Regra prática para vias de desacoplamento: colocar o capacitor o mais próximo possível do pino do regulador; use vias curtas e múltiplas para reduzir indutância série. Via stitching em bordas e ao longo de planos reduz emissões radiadas.

Roteie sinais de alta velocidade com impedância controlada, minimize cruzamentos entre trilhas de clock e trilhas sensíveis e mantenha retorno direto sob a trilha para impedir laços.

PDN e dimensionamento de desacoplamento

Projete a PDN para um target impedance que mantenha ripple e variações dentro das margens de estabilidade do regulador. Use combinação de MLCCs para cobrir faixas de frequência (p.ex. 0.01µF para altas freq, 1µF para médias, 10µF para transientes).

Distribua capacitores em uma hierarquia: local (ao lado do pino), de placa e bulk (próximo à entrada do conversor). Calcule ESR/ESL para garantir amortecimento adequado e evitar ressonâncias indesejadas.

Ferramentas de CAD permitem inserir regras de design para automação de placement/DRC e gerar relatórios de impedância que facilitam revisão antes de fabricação.

Componentes, filtragem e técnicas avançadas de mitigação de ruído

Seleção de componentes e topologias de filtro

Capacitores MLCC são padrão por baixa ESL/ESR; porém atenção à variação de capacitância com tensão DC e temperatura (nome da dielétrica). Ferrites e beads são úteis para supressão em caminho único, enquanto chokes common-mode atuam bem contra ruído diferencial/conduzido.

Topologias de filtro comuns: RC para altas frequências, LC para atenuação mais forte em faixas específicas, PI para requisitos de rejeição mais agressivos. TVS protegem contra transientes na entrada de alimentação.

Critérios de seleção: atenuação desejada (dB), tensão de operação, corrente DC, perda por temperatura e footprint para montagem. Trade-offs: latência, queda de tensão e custo.

Exemplos práticos de implementação

Para um conversor DC-DC buck com saída sensível, use um filtro LC local, MLCC no pino de saída, bead na linha de entrada e choke common-mode se houver cabos externos. Documente medidas de melhoria (dB de redução no espectro).

Em interfaces de alta velocidade, adote termination adequada (AC/DC, series/shunt), vias de escape e ground pour com stitching para controlar return path. Para fontes Mean Well usadas em aplicações industriais, combinar filtros de linha com PFC reduz ruído condutivo antes da PDN.

Teste variantes no protótipo: medir antes/depois de cada alteração para validar trade-offs (por ex.: aumento de ripple vs. redução de emissão).

Simulação, verificação e erros comuns no caminho para estabilidade — comparações e soluções

Ferramentas de simulação e fluxo de verificação

Use SPICE para comportamento de malhas e transient response; simulação de Power Integrity para target impedance e análise de decoupling; EM 3D para modelagem de radiação e acoplamento entre planos. Integre resultados ao ECM/DFM antes da pilotagem.

Comparações importantes: split plane vs single plane — split plane pode isolar ruídos, mas cria caminhos de retorno que aumentam EMI se não for bem planejado; single solid plane costuma ser preferível para retorno contínuo.

Verifique com simulações e depois valide no protótipo: correlacione formas de onda e espectros; ajuste modelos de capacitor com ESR/ESL medidos para aumentar precisão de simulação.

Erros frequentes e correções rápidas

Erros comuns: capacitores de desacoplamento posicionados longe, uso excessivo de vias únicas em power, planos fragmentados e falta de vias de retorno. Correções rápidas incluem reposicionar capacitores, adicionar stitching e reduzir loop area.

Outro erro: confiar apenas em cálculo teórico de target impedance sem validar com medição PDN analyzer; sempre confirmar em bancada. Além disso, não subestime efeitos de embalagem (wire bonds, BGA) na integridade do sinal.

Estabeleça um ciclo iteração: simulação → protótipo → medição → ajuste, documentando mudanças para acelerar futuros projetos.

Checklist final, guias de referência e roadmap aplicado para projetos futuros estabilidade e ruído em PCBs

Checklist acionável para estabilização e baixo ruído

- Definir target impedance por faixa de frequência antes do layout.

- Posicionar capacitores de desacoplamento diretamente ao pino do IC (vias curtas).

- Garantir retorno contínuo sob trilhas de alta velocidade; evitar splits desnecessários.

- Implementar via stitching e planos sólidos; evitar longos loops de corrente.

- Validar com oscilloscope diferencial, near-field probe e PDN analyzer.

Use este checklist como parte do DFX do produto.

Valores típicos e testes obrigatórios

Valores de referência (orientativos):

- Capacitores MLCC: 0.01µF–1µF local + 4.7µF–22µF bulk

- Target impedance: < tens de mΩ para rails de alimentação sensíveis (depende do corrente)

- Ripple permitido: especificar conforme tolerância do sistema (mVpp para ADCs)

Testes obrigatórios: transient response, ripple, imunidade IEC 61000-4-6, emissão radiada conforme CISPR/EN. Para fontes, consulte modelos Mean Well para dimensionar filtros e PFC.

Roadmap de melhoria contínua

- Estabelecer métricas e objetivos no RFQ (target impedance, jitter, SNR).

- Incluir regras de layout no template CAD e automatizar DRC para PDN.

- Simular PDN e validar no protótipo com medidas replicáveis.

- Integrar feedback de testes EMC e ajustar filtros/power sequencing.

Para referência prática sobre filtros e fontes consulte artigos no blog (ex.: https://blog.meanwellbrasil.com.br/filtragem-emi, https://blog.meanwellbrasil.com.br/guia-de-pdn) e explore nossas soluções de fontes industriais em https://www.meanwellbrasil.com.br/produtos. Se precisa de uma recomendação de produto para sua aplicação, veja as opções disponíveis em https://www.meanwellbrasil.com.br/produtos/fontes-industriais.

Conclusão

Controlar estabilidade e ruído em PCBs é um requisito técnico e de negócio: reduz riscos de certificação, aumenta MTBF e melhora desempenho de produto. Aplicando práticas de PDN, layout, filtragem e verificação, você converte métricas abstratas (target impedance, jitter, SNR) em resultados práticos e repetíveis.

Este artigo ofereceu um roteiro completo — desde identificação de fontes até simulação e otimização — para que sua equipe implemente melhorias de forma sistemática. Para aprofundar com artigos técnicos e estudos de caso práticos, visite nosso blog: https://blog.meanwellbrasil.com.br/.

Ficou alguma dúvida técnica ou quer que eu gere um checklist CAD/DRC específico para seu projeto? Comente abaixo — respondo com recomendações práticas e, se desejar, posso transformar cada seção em diagramas e scripts de simulação.